## **General Description**

The MAX5200–MAX5203 serial input, voltage-output, 16-bit digital-to-analog converters (DACs) provide monotonic 16-bit output over temperature without any adjustments. The MAX5200/MAX5201 operate from a +5V single power supply featuring an internal reference of +2.5V and an internal gain of 2, while the MAX5202/MAX5203 operate from a +3V or +3.3V single power supply featuring an internal reference of +1.5V and an internal reference of +1.5V and an internal gain of 2. The MAX5200–MAX5203 DAC output range is typically from 0 to V<sub>DD</sub>.

The MAX5200–MAX5203 feature a hardware reset input  $\overline{(CLR)}$  that, when pulled low, clears the output to zero code 0000 hex (MAX5201/MAX5203) or resets the output to midscale code 8000 hex (MAX5200/MAX5202).

The 3-wire serial interface is compatible with SPITM/QSPITM/MICROWIRETM. All devices have a low-power shutdown mode that reduces the supply current consumption to  $1\mu A$ .

The MAX5200–MAX5203 are available in a space-saving 10-pin  $\mu$ MAX<sup>®</sup> package and are guaranteed over the extended temperature range (-40°C to +105°C). Refer to the MAX5204–MAX5207 data sheet for external reference versions.

## **Applications**

Low-Cost VCO/VCXO Frequency Control Industrial Process Control High-Resolution Offset Adjustment

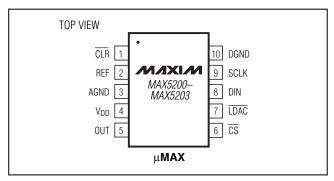

# **Pin Configuration**

SPI/QSPI are trademarks of Motorola, Inc.

MICROWIRE is a trademark of National Semiconductor Corp. µMAX is a registered trademark of Maxim Integrated Products, Inc.

# Rail-to-Rail Output Amplifier

Single-Supply Operation

+5V (MAX5200/MAX5201)

+3V, +3.3V (MAX5202/MAX5203)

10-Pin 5mm × 3mm µMAX Package

Guaranteed 16-Bit Monotonic

Internal Reference

- Low Power Consumption: 0.8mA

- ♦ Shutdown Mode Reduces Supply Current to 1µA

- SPI/QSPI/MICROWIRE-Compatible 3-Wire Serial Interface

- Power-On-Reset Sets Output to Midscale (MAX5200/MAX5202) Zero Scale (MAX5201/MAX5203)

## **Ordering Information**

| PART        | TEMP RANGE      | PIN-PACKAGE |

|-------------|-----------------|-------------|

| MAX5200AEUB | -40°C to +105°C | 10 µMAX     |

| MAX5200BEUB | -40°C to +105°C | 10 µMAX     |

| MAX5200ACUB | 0°C to +70°C    | 10 µMAX     |

| MAX5201AEUB | -40°C to +105°C | 10 µMAX     |

| MAX5201BEUB | -40°C to +105°C | 10 µMAX     |

| MAX5201ACUB | 0°C to +70°C    | 10 µMAX     |

| MAX5202AEUB | -40°C to +105°C | 10 µMAX     |

| MAX5202BEUB | -40°C to +105°C | 10 µMAX     |

| MAX5202ACUB | 0°C to +70°C    | 10 µMAX     |

| MAX5203AEUB | -40°C to +105°C | 10 µMAX     |

| MAX5203BEUB | -40°C to +105°C | 10 µMAX     |

| MAX5203ACUB | 0°C to +70°C    | 10 µMAX     |

Selector Guide appears at end of data sheet.

MAX5200-MAX5203

Features

#

\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to AGND, DGND0.3V to +6V<br>AGND to DGND0.3V to +0.3V |

|-----------------------------------------------------------------------|

| REF, OUT to AGND0.3V to $(V_{DD} + 0.3V)$                             |

| CLR, LDAC, SCLK, DIN, CS to DGND0.3V to (V <sub>DD</sub> + 0.3V)      |

| Maximum Current into Any Pin50mA                                      |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                 |

| 10-Pin µMAX (derate 5.6mW/°C above +70°C)444.4mW                      |

| Operating | Temperature | Ranges |

|-----------|-------------|--------|

|-----------|-------------|--------|

| MAX520_CUB                        | 0°C to +70°C   |

|-----------------------------------|----------------|

| MAX520_EUB                        | 40°C to +105°C |

| Junction Temperature              | +150°C         |

| Storage Temperature Range         | 60°C to +150°C |

| Lead Temperature (soldering, 10s) | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS—MAX5200/MAX5201**

$(V_{DD} = +4.75V \text{ to } +5.25V, f_{SCLK} = 10MHz (50\% \text{ duty cycle}), \text{ output load} = 10k\Omega \text{ in parallel with } 250pF, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.)$

| PARAMETER                             | SYMBOL | CONDITIONS                                                                                                                        | MIN | ТҮР                     | МАХ  | UNITS  |

|---------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------|------|--------|

| STATIC PERFORMANCE (Note              | 1)     | •                                                                                                                                 |     |                         |      |        |

| Resolution                            | Ν      |                                                                                                                                   | 16  |                         |      | Bits   |

|                                       |        | MAX520_AEUB                                                                                                                       |     | ±10                     | ±20  |        |

| Integral Nonlinearity (Note 2)        | INL    | MAX520_ACUB                                                                                                                       |     | ±10                     | ±20  | LSB    |

|                                       |        | MAX520_BEUB                                                                                                                       |     | ±20                     | ±40  |        |

| Differential Nonlinearity<br>(Note 2) |        | MAX520_A_UB (Note 3)                                                                                                              |     |                         | ±1   |        |

|                                       | DNL    | MAX520_BEUB (0°C to +105°C) (Note 3)                                                                                              |     |                         | ±1   | LSB    |

|                                       |        | MAX520_BEUB (-40°C to 0°C)                                                                                                        |     |                         | ±2   |        |

| Offset Error                          |        | Inferred from measurement at 1C00 hex and FFFF hex                                                                                |     | ±3                      | ±25  | mV     |

| Gain Error                            | GE     | Within DAC output range (Note 4)                                                                                                  |     | ±0.01                   | ±1   | %FSR   |

| Power-Supply Rejection                | PSR    | $V_{DD} = 5V \pm 5\%$ , midscale input                                                                                            |     | ±0.06                   | ±0.5 | mV/V   |

| DYNAMIC PERFORMANCE                   | •      |                                                                                                                                   |     |                         |      |        |

| DAC Output Range                      |        | (Note 2)                                                                                                                          |     | 0 to<br>V <sub>DD</sub> |      | V      |

| Output-Voltage Slew Rate              | SR     |                                                                                                                                   |     | 0.6                     |      | V/µs   |

| Output Settling Time                  |        | To ±1LSB of FS,<br>V <sub>STEP</sub> = $0.25 \times V_{REF}$ to $0.75 \times V_{REF}$                                             |     | 25                      |      | μs     |

| Output Noise                          |        | DAC code = 8400 hex, 10kHz                                                                                                        |     | 175                     |      | nV/√Hz |

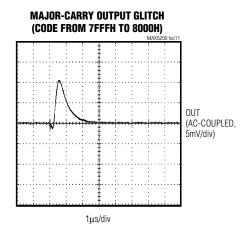

| DAC Glitch Impulse                    |        | Major carry transition (code 7FFF hex to code 8000 hex)                                                                           |     | 10                      |      | nV∙s   |

| Digital Feedthrough                   |        | $      Code = 0000 \text{ hex; } \overline{CS} = V_{DD}; \\       \overline{LDAC} = 0; \text{ SCLK, DIN} = 0 \text{ or } V_{DD} $ |     | 10                      |      | nV⋅s   |

| Wake-Up Time                          |        | From software shutdown to 90% of output code = FFFF hex, $C_{REF} = 0.1 \mu F$                                                    |     | 50                      |      | μs     |

| Power-Up Time                         |        | From power applied to 90% of output code = FFFF hex                                                                               |     | 10                      |      | ms     |

MAX5200-MAX5203

## ELECTRICAL CHARACTERISTICS—MAX5200/MAX5201 (continued)

$(V_{DD} = +4.75V \text{ to } +5.25V, f_{SCLK} = 10MHz$  (50% duty cycle), output load = 10k $\Omega$  in parallel with 250pF, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                                           | SYMBOL             | CONDITIONS                                          | MIN  | TYP | MAX  | UNITS    |

|-----------------------------------------------------|--------------------|-----------------------------------------------------|------|-----|------|----------|

| INTERNAL REFERENCE                                  | •                  | ·                                                   | •    |     |      | •        |

| V <sub>REF</sub> Output Voltage                     |                    | $T_A = +25^{\circ}C$                                | 2.48 | 2.5 | 2.52 | V        |

|                                                     |                    | $T_A = 0^{\circ}C \text{ to } +70^{\circ}C$         |      | ±15 |      | 10.00.00 |

| V <sub>REF</sub> Tempco                             |                    | $T_{A} = -40^{\circ}C \text{ to } +105^{\circ}C$    |      | ±20 |      | ppm/°C   |

| DIGITAL INPUTS (DIN, SCLK, CS,                      | CLR, LDAC          | ā)                                                  |      |     |      |          |

| Input High Voltage                                  | VIH                |                                                     | 2.4  |     |      | V        |

| Input Low Voltage                                   | VIL                |                                                     |      |     | 0.8  | V        |

| Input Hysteresis                                    | VHYST              |                                                     |      | 200 |      | mV       |

| Input Leakage                                       | lin                | Digital inputs = 0 or $V_{DD}$                      |      |     | ±1   | μA       |

| Input Capacitance                                   | CIN                |                                                     |      | 15  |      | pF       |

| POWER REQUIREMENTS                                  |                    |                                                     |      |     |      |          |

| Positive Power Supply                               | V <sub>DD</sub>    |                                                     | 4.75 |     | 5.25 | V        |

| Positive Supply Current                             | IDD                | All digital inputs at 0 or V <sub>DD</sub> (Note 5) |      | 0.8 | 1.5  | mA       |

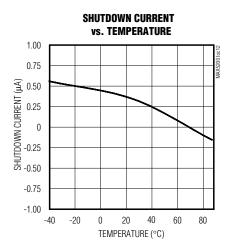

| Shutdown Supply Current                             | ISHDN              | All digital inputs at 0 or V <sub>DD</sub>          |      | 1   | 10   | μA       |

| TIMING CHARACTERISTICS                              |                    |                                                     |      |     |      |          |

| SCLK Frequency                                      | <b>f</b> SCLK      |                                                     |      |     | 10   | MHz      |

| SCLK Clock Period                                   | tCP                |                                                     | 100  |     |      | ns       |

| SCLK Pulse Width High                               | t <sub>CH</sub>    |                                                     | 40   |     |      | ns       |

| SCLK Pulse Width Low                                | tCL                |                                                     | 40   |     |      | ns       |

| DIN Setup Time                                      | t <sub>DS</sub>    |                                                     | 40   |     |      | ns       |

| DIN Hold Time                                       | tDH                |                                                     | 0    |     |      | ns       |

| CS Fall to SCLK Rise Setup Time                     | tcss               |                                                     | 40   |     |      | ns       |

| SCLK Rise to $\overline{\text{CS}}$ Rise Hold Time  | tCSH               |                                                     | 0    |     |      | ns       |

| SCLK Rise to $\overline{CS}$ Fall Ignore            | tcso               |                                                     | 10   |     |      | ns       |

| CS Rise to SCLK Rise Ignore                         | tCS1               |                                                     | 40   |     |      | ns       |

| LDAC Pulse Width                                    | <b>t</b> LDAC      |                                                     | 40   |     |      | ns       |

| CS Rise to LDAC Low Setup                           | t <sub>LDACS</sub> |                                                     | 40   |     |      | ns       |

| SCLK Fall to $\overline{CS}$ Fall Ignore            | tcsol              |                                                     | 10   |     |      | ns       |

| $\overline{\text{CS}}$ Pulse Width Low for Shutdown | tcswl              |                                                     | 40   |     |      | ns       |

| CS Pulse Width High                                 | tcswh              |                                                     | 100  |     |      | ns       |

### ELECTRICAL CHARACTERISTICS—MAX5202/MAX5203

$(V_{DD} = +2.7V \text{ to } +3.6V, \text{ } \text{f}_{SCLK} = 10 \text{MHz} (50\% \text{ duty cycle}), \text{ output load} = 10 \text{k}\Omega \text{ in parallel with } 250 \text{pF}, \text{ } \text{T}_{A} = \text{T}_{MIN} \text{ to } \text{T}_{MAX}, \text{ unless otherwise noted}. Typical values are at T_{A} = +25^{\circ}\text{C}.)$

| PARAMETER                             | SYMBOL | CONDITIONS                                                                                                                                                                                                                          | MIN | ТҮР                     | MAX  | UNITS             |

|---------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------|------|-------------------|

| STATIC PERFORMANCE (Note              | 1)     |                                                                                                                                                                                                                                     |     |                         |      |                   |

| Resolution                            | Ν      |                                                                                                                                                                                                                                     | 16  |                         |      | Bits              |

|                                       |        | MAX520_AEUB                                                                                                                                                                                                                         |     | ±10                     | ±20  |                   |

| Integral Nonlinearity (Note 2)        | INL    | MAX520_ACUB                                                                                                                                                                                                                         |     | ±10                     | ±20  | LSB               |

|                                       |        | MAX520_BEUB                                                                                                                                                                                                                         |     | ±20                     | ±40  |                   |

| Differential Nonlinearity<br>(Note 2) |        | MAX520_A_UB (Note 3)                                                                                                                                                                                                                |     |                         | ±1   |                   |

|                                       | DNL    | MAX520_BEUB (0°C to +105°C) (Note 3)                                                                                                                                                                                                |     |                         | ±1   | LSB               |

|                                       |        | MAX520_BEUB (-40°C to 0°C)                                                                                                                                                                                                          |     |                         | ±2   |                   |

| Offset Error                          |        | Inferred from measurement at 3800 hex and FFFF hex                                                                                                                                                                                  |     | ±3                      | ±25  | mV                |

| Gain Error                            | GE     | Within DAC output range (Note 4)                                                                                                                                                                                                    |     | ±0.01                   | ±1.0 | %FSR              |

| Power-Supply Rejection                | PSR    | $V_{DD} = 3V \pm 10\%$ , midscale input                                                                                                                                                                                             |     | ±0.06                   | ±0.5 | mV/V              |

| DYNAMIC PERFORMANCE                   |        |                                                                                                                                                                                                                                     |     |                         |      |                   |

| DAC Output Range                      |        | (Note 2)                                                                                                                                                                                                                            |     | 0 to<br>V <sub>DD</sub> |      | V                 |

| Voltage-Output Slew Rate              | SR     |                                                                                                                                                                                                                                     |     | 0.6                     |      | V/µs              |

| Output Settling Time                  |        | To $\pm 1$ LSB of FS,<br>V <sub>STEP</sub> = 0.25 × V <sub>REF</sub> to 0.75 × V <sub>REF</sub>                                                                                                                                     |     | 25                      |      | μs                |

| Output Noise                          |        | Code = 8400 hex, 10kHz                                                                                                                                                                                                              |     | 175                     |      | nV/√Hz            |

| Reference Feedthrough                 |        | Code = 0000 hex at 100kHz, V <sub>REF</sub> = 1V <sub>P-P</sub>                                                                                                                                                                     |     | 1                       |      | mV <sub>P-P</sub> |

| DAC Glitch Impulse                    |        | Major carry transition (code 7FFF hex to code 8000 hex)                                                                                                                                                                             |     | 10                      |      | nV∙s              |

| Digital Feedthrough                   |        | $\label{eq:code} \begin{array}{l} \mbox{Code} = 0000 \mbox{ hex; } \overline{\mbox{CS}} = \mbox{V}_{\mbox{DD}}; \\ \hline \mbox{LDAC} = 0; \mbox{SCLK}, \mbox{DIN} = 0 \mbox{ or } \mbox{V}_{\mbox{DD}} \mbox{ levels} \end{array}$ |     | 10                      |      | nV∙s              |

| Wake-Up Time                          |        | From software shutdown to 90% of output<br>code = FFFF hex                                                                                                                                                                          |     | 50                      |      | μs                |

| Power-Up Time                         |        | From power applied to 90% of output code = FFFF hex                                                                                                                                                                                 |     | 10                      |      | ms                |

M/X/M

### ELECTRICAL CHARACTERISTICS—MAX5202/MAX5203 (continued)

$(V_{DD} = +2.7V \text{ to } +3.6V, f_{SCLK} = 10MHz (50\% \text{ duty cycle}), \text{ output load} = 10k\Omega \text{ in parallel with } 250pF, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.)$

| PARAMETER                                           | SYMBOL            | CONDITIONS                                          | MIN  | ТҮР | MAX  | UNITS     |

|-----------------------------------------------------|-------------------|-----------------------------------------------------|------|-----|------|-----------|

| INTERNAL REFERENCE                                  | -                 | ·                                                   | •    |     |      |           |

| V <sub>REF</sub> Output Voltage                     |                   | $T_A = +25^{\circ}C$                                | 1.46 | 1.5 | 1.54 | V         |

|                                                     |                   | $T_A = 0^{\circ}C \text{ to } +70^{\circ}C$         |      | ±15 |      | 10.10.000 |

| V <sub>REF</sub> Tempco                             |                   | $T_A = -40^{\circ}C \text{ to } +105^{\circ}C$      |      | ±20 |      | ppm/°C    |

| DIGITAL INPUTS (DIN, SCLK, CS                       | , CLR, LDAC       | 5)                                                  |      |     |      |           |

| Input High Voltage                                  | VIH               |                                                     | 2.1  |     |      | V         |

| Input Low Voltage                                   | VIL               |                                                     |      |     | 0.6  | V         |

| Input Hysteresis                                    | V <sub>HYST</sub> |                                                     |      | 200 |      | mV        |

| Input Leakage                                       | lin               | Digital inputs = 0 or $V_{DD}$                      |      |     | ±1   | μA        |

| Input Capacitance                                   | CIN               |                                                     |      | 15  |      | pF        |

| POWER REQUIREMENTS                                  |                   |                                                     |      |     |      |           |

| Positive Power Supply                               | V <sub>DD</sub>   |                                                     | 2.7  |     | 3.6  | V         |

| Positive Supply Current                             | IDD               | All digital inputs at 0 or V <sub>DD</sub> (Note 5) |      | 0.8 | 1.5  | mA        |

| Shutdown Supply Current                             | ISHDN             | All digital inputs at 0 or V <sub>DD</sub>          |      | 1   | 10   | μΑ        |

| TIMING CHARACTERISTICS                              |                   |                                                     |      |     |      |           |

| SCLK Frequency                                      | <b>f</b> SCLK     |                                                     |      |     | 10   | MHz       |

| SCLK Clock Period                                   | tCP               |                                                     | 100  |     |      | ns        |

| SCLK Pulse Width High                               | tсн               |                                                     | 40   |     |      | ns        |

| SCLK Pulse Width Low                                | tCL               |                                                     | 40   |     |      | ns        |

| DIN Setup Time                                      | t <sub>DS</sub>   |                                                     | 40   |     |      | ns        |

| DIN Hold Time                                       | tDН               |                                                     | 0    |     |      | ns        |

| CS Fall to SCLK Rise Setup Time                     | tcss              |                                                     | 40   |     |      | ns        |

| SCLK Rise to $\overline{\text{CS}}$ Rise Hold Time  | tCSH              |                                                     | 0    |     |      | ns        |

| SCLK Rise to $\overline{CS}$ Fall Ignore            | tcso              |                                                     | 10   |     |      | ns        |

| CS Rise to SCLK Rise Ignore                         | tCS1              |                                                     | 40   |     |      | ns        |

| LDAC Pulse Width                                    | <b>t</b> LDAC     |                                                     | 40   |     |      | ns        |

| CS Rise to LDAC Low Setup                           | <b>t</b> LDACS    |                                                     | 40   |     |      | ns        |

| SCLK Fall to $\overline{CS}$ Fall Ignore            | tcsol             |                                                     | 10   |     |      | ns        |

| $\overline{\text{CS}}$ Pulse Width Low for Shutdown | tcswL             |                                                     | 40   |     |      | ns        |

| CS Pulse Width High                                 | t <sub>CSWH</sub> |                                                     | 100  |     |      | ns        |

Note 1: Static performance tested at  $V_{DD}$  = +5.0V (MAX5200/MAX5201) and at  $V_{DD}$  = +3.0V (MAX5202/MAX5203).

Note 2: INL and DNL are guaranteed for outputs between 0.5V to ( $V_{DD}$  - 0.5V).

Note 3: Guaranteed monotonic.

Note 4:  $V_{REF} = 2.5V$  (MAX5200/MAX5201) and  $V_{REF} = 1.5V$  (MAX5202/MAX5203).

**Note 5:**  $R_L = \infty$ , digital inputs are at  $V_{DD}$  or DGND.

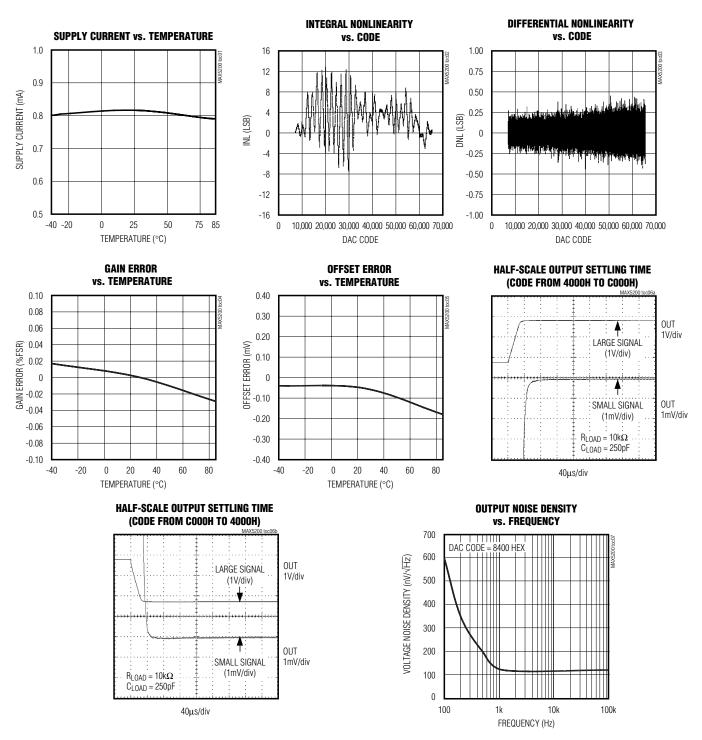

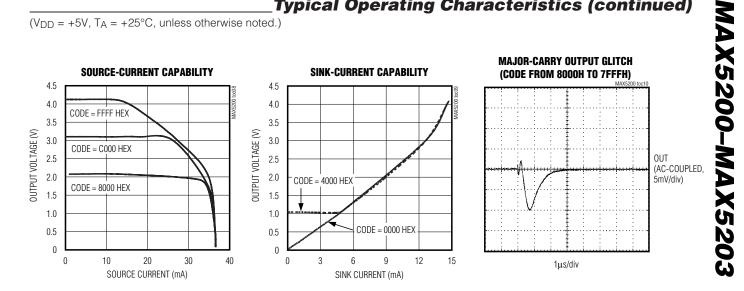

$(V_{DD} = +5V, T_A = +25^{\circ}C, unless otherwise noted.)$

## **Typical Operating Characteristics**

MAX5200-MAX5203

## **Typical Operating Characteristics (continued)**

$(V_{DD} = +5V, T_A = +25^{\circ}C, unless otherwise noted.)$

**Pin Description**

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                   |

|-----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | CLR             | Reset DAC Active-Low Input. Pull $\overline{\text{CLR}}$ low to reset the DAC output to midscale output (8000 hex) for MAX5200/MAX5202 and to zero-scale output (0000 hex) for MAX5201/MAX5203. For normal operation, connect $\overline{\text{CLR}}$ to V <sub>DD</sub> . |

| 2   | REF             | Reference Voltage Output. Provides a +2.5V (MAX5200/MAX5201) or +1.5V (MAX5202/MAX5203) nominal output. For improved noise performance, bypass with a minimum 0.1µF capacitor to AGND.                                                                                     |

| 3   | AGND            | Analog Ground                                                                                                                                                                                                                                                              |

| 4   | V <sub>DD</sub> | Positive Supply Voltage. Bypass $V_{DD}$ to AGND with a $10\mu F$ capacitor in parallel with a $0.1\mu F$ capacitor.                                                                                                                                                       |

| 5   | OUT             | DAC Output Voltage                                                                                                                                                                                                                                                         |

| 6   | CS              | Active-Low Chip-Select Input                                                                                                                                                                                                                                               |

| 7   | LDAC            | Load DAC Input                                                                                                                                                                                                                                                             |

| 8   | DIN             | Serial Data Input                                                                                                                                                                                                                                                          |

| 9   | SCLK            | Serial Clock Input. Duty cycle must be 40% to 60%.                                                                                                                                                                                                                         |

| 10  | DGND            | Digital Ground                                                                                                                                                                                                                                                             |

# **Detailed Description**

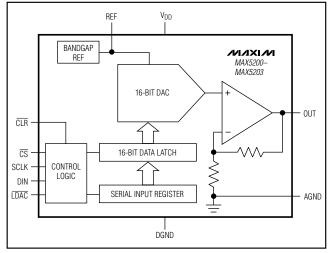

The MAX5200–MAX5203 serial 16-bit, voltage-output DACs are easily configured with a 3-wire serial interface. These devices offer full 16-bit performance with less than  $\pm 20$ LSB integral linearity error and less than  $\pm 1$ LSB differential linearity error, thus ensuring monotonic performance. Serial data transfer minimizes the number of package pins required. The MAX5200–MAX5203 include control-logic circuitry, a 16-bit data-in shift register, and a DAC register. In addition, these devices employ a precision-bandgap reference and trimmed internal resistors to produce a gain of 2V/V, maximizing the output voltage swing. The MAX5200–MAX5203 output is buffered and the full-scale output voltage is 2 × VREF.

The MAX5200–MAX5203 feature a hardware reset input (CLR) that, when pulled low, clears the DAC output to zero code 0000H (MAX5201/MAX5203) or resets the DAC output to midscale code 8000 hex (MAX5200/MAX5202). For normal operation, connect CLR to VDD.

#### Internal Reference

The MAX5200/MAX5201 (+5V supply) include an internal reference of 2.5V while the MAX5202/MAX5203 (+3V supply) include an internal reference of 1.5V. The DAC output range is from 0 to  $2 \times V_{REF}$ . Do not drive external circuitry from this reference. To improve DAC output noise performance, bypass with a low leakage 0.1µF minimum capacitor to AGND.

Figure 1. MAX5200–MAX5203 Simplified Functional Diagram

#### **Digital Interface**

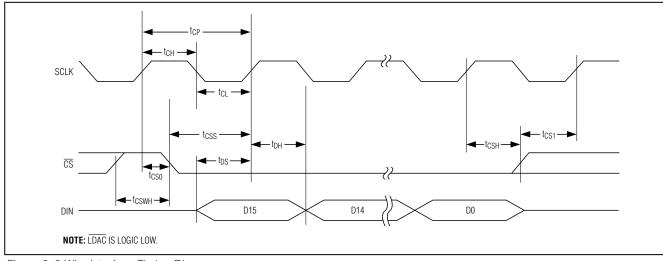

The MAX5200–MAX5203 digital interface is a standard 3-wire connection compatible with SPI/QSPI/ MICROWIRE and most DSP interfaces. All of the digital input pins (CS, SCLK, DIN, CLR, and LDAC) are TTL compatible. SCLK can accept clock frequencies as high as 10MHz for a +5V supply and 10MHz for a +3V or +3.3V supply.

One of two methods can be used when interfacing and updating the MAX5200–MAX5203. The first requires three digital inputs:  $\overline{CS}$ , DIN, and SCLK (Figure 2). The active-low chip-select input ( $\overline{CS}$ ) enables the serial

Figure 2. 3-Wire Interface Timing Diagram

data loading at the data input (DIN). Pull  $\overline{CS}$  low and clock in each bit of the 16-bit digital word on the rising edge of the serial clock (SCLK). Two 8-bit bytes can be used, and do not require any additional time between them. Pulling  $\overline{CS}$  high after loading the 16-bit word transfers that code into the DAC register and then updates the output. If  $\overline{CS}$  is not kept low during the entire loading of the 16-bit word, data is corrupted. In this case, a new 16-bit word must be loaded.  $\overline{LDAC}$  must be kept low at all times for the above instructions.

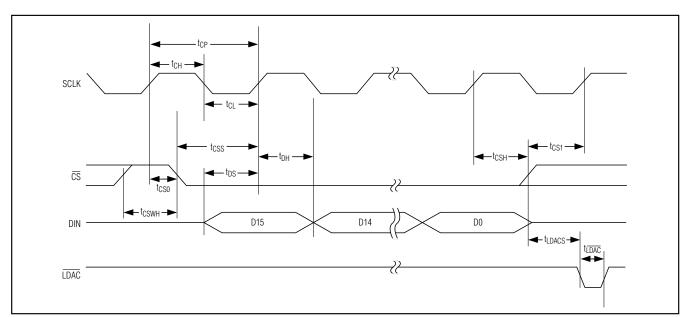

An alternate method of interfacing and updating the MAX5200–MAX5203 can be done with a fourth digital input, the active-low load DAC (LDAC). LDAC allows the output to update asynchronously after CS goes high. It is useful when updating multiple MAX5200–MAX5203s synchronously when sharing a single LDAC and CS line. LDAC must be kept high at all times during the data-loading sequence and must only be asserted when CS is high. Asserting LDAC when CS is low can cause corrupted data. To operate the MAX5200–MAX5203 using LDAC, pull LDAC high, pull CS low, load the 16-bit word as described in the previous paragraph, and pull CS high again. Following these commands, the DAC output only updates when LDAC is asserted low (Figure 3).

#### Shutdown Mode

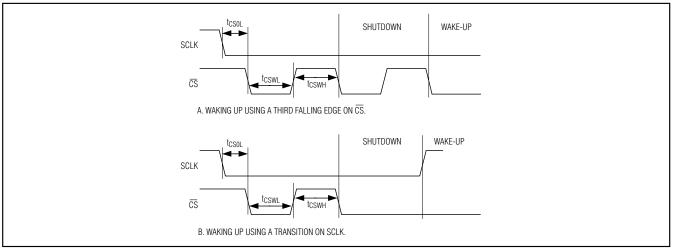

The low-power shutdown mode reduces supply current to typically  $1\mu$ A and a maximum of  $10\mu$ A. Shutdown mode is not activated through command words, as is common among D/A converters. These devices require careful manipulation of  $\overline{CS}$  and SCLK (Figure 4).

#### Shutting Down

To shut down the MAX5200–MAX5203, change the state of SCLK (either a high to low or low to high transition can be used) and pulse two falling  $\overline{CS}$  edges. In order to keep the device in shutdown mode, SCLK **must** not change state. SCLK must remain in the state it is in after the two  $\overline{CS}$  pulses.

#### Waking Up

There are two methods to wake up the MAX5200–MAX5203. Pulse one falling  $\overline{CS}$  edge or transition SCLK. It takes 50µs typically from the  $\overline{CS}$  falling edge or SCLK transition for the DAC to return to normal operation.

#### **Power-On Reset**

The MAX5200–MAX5203 have a power-on reset circuit to set the DAC's output to a known state when V<sub>DD</sub> is first applied. The MAX5200/MAX5202 reset to midscale (code 8000 hex) upon power-up. The MAX5201/MAX5203 reset to zero scale (code 0000 hex) upon power-up. This ensures that unwanted output voltages do not occur immediately following a system power-up, such as a loss of power. It is required to apply V<sub>DD</sub> first before any other inputs (DIN, SCLK, CLR, LDAC, and CS).

Figure 3. 4-Wire Interface Timing Diagram

Figure 4. Shutdown Timing

# **Applications Information**

#### Power-Supply and Bypassing Considerations

Bypass the power supply with a  $10\mu$ F capacitor in parallel with a  $0.1\mu$ F capacitor to AGND. Minimize lead lengths to reduce lead inductance. If noise becomes an issue, use shielding and/or ferrite beads to increase isolation.

#### **Output Buffer**

The MAX5200–MAX5203 include low-offset, low-noise buffers enabling the output to source 15mA or sink 5mA. The output buffer operates at a slew rate of 0.6V/µs. With a 1/4 FS to 3/4 FS output transition, the buffer output typically settles to 1 LSB in less than 25µs. The MAX5200–MAX5203 output buffers provide a low 0.2 $\Omega$  typical output impedance. The MAX5200–MAX5203 buffer amplifiers typically produce 175nV/vHz noise at 10kHz.

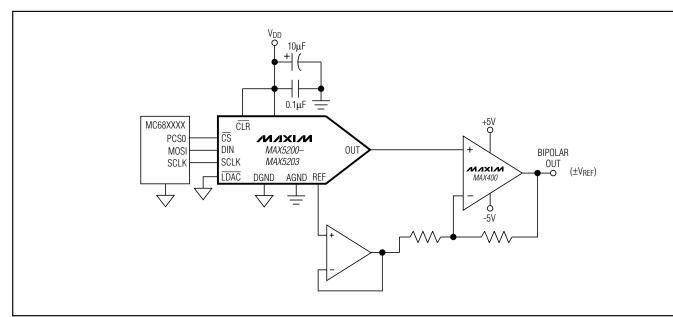

Figure 5. MAX5200–MAX5203 Typical Operating Circuit—Bipolar Output

### Table 1. Bipolar Code Table

| DAC LATCH CONTENTS |          | ANALOG OUTPUT, VOUT                   |

|--------------------|----------|---------------------------------------|

| MSB                | LSB      | ANALOG COTPOT, VOUT                   |

| 1111 1111 111      | 11 1111  | +V <sub>REF</sub> × (32,767 / 32,768) |

| 1000 0000 000      | 00 0001  | +V <sub>REF</sub> × (1 / 32,768)      |

| 1000 0000 000      | 0000 00  | OV                                    |

| 0111 1111 111      | 1 1111   | -V <sub>REF</sub> × (1 / 32,768)      |

| 0000 0000 000      | 0000 000 | -V <sub>REF</sub> × (32,768 / 32,768) |

#### **Bipolar Configuration**

The MAX5200–MAX5203 are designed for unipolar operation, but can be used in bipolar applications with an external amplifier and resistors. Figure 5 shows the MAX5200–MAX5203 configured for bipolar operation. The op amp is set for unity gain. Table 1 lists the offset binary code for this circuit. The output voltage range is  $\pm V_{REF}$ .

#### **Layout Considerations**

Digital and AC transient signals coupling to AGND can create noise at the output. Connect AGND to the highest quality ground available. Use proper grounding techniques, such as a multilayer board with a lowinductance ground plane. Wire-wrapped boards and sockets are not recommended. For optimum system performance, use printed circuit (PC) boards with separate analog and digital ground planes. Connect the two ground planes together at the low-impedance power-supply source. Connect DGND and AGND pins together at the IC. The best ground connection is achieved by connecting the DAC's DGND and AGND together, and then connecting that point to the system analog ground plane. If the DAC's DGND is connected to the system digital ground, digital noise can get through the DAC's analog portion.

## Chip Information

TRANSISTOR COUNT: 8764 PROCESS: BICMOS

# Selector Guide

| PART        | INTEGRAL<br>NONLINEARITY<br>(LSB, MAX) | SUPPLY VOLTAGE<br>RANGE (V) | REFERENCE INPUT<br>RANGE (V) | POWER-ON-RESET<br>VALUE |

|-------------|----------------------------------------|-----------------------------|------------------------------|-------------------------|

| MAX5200AEUB | 20                                     | 4.75 to 5.25                | 2.5                          | Midscale                |

| MAX5200ACUB | 20                                     | 4.75 to 5.25                | 2.5                          | Midscale                |

| MAX5200BEUB | 40                                     | 4.75 to 5.25                | 2.5                          | Midscale                |

| MAX5201AEUB | 20                                     | 4.75 to 5.25                | 2.5                          | Zero                    |

| MAX5201ACUB | 20                                     | 4.75 to 5.25                | 2.5                          | Zero                    |

| MAX5201BEUB | 40                                     | 4.75 to 5.25                | 2.5                          | Zero                    |

| MAX5202AEUB | 20                                     | 2.7 to 3.6                  | 1.5                          | Midscale                |

| MAX5202ACUB | 20                                     | 2.7 to 3.6                  | 1.5                          | Midscale                |

| MAX5202BEUB | 40                                     | 2.7 to 3.6                  | 1.5                          | Midscale                |

| MAX5203AEUB | 20                                     | 2.7 to 3.6                  | 1.5                          | Zero                    |

| MAX5203ACUB | 20                                     | 2.7 to 3.6                  | 1.5                          | Zero                    |

| MAX5203BEUB | 40                                     | 2.7 to 3.6                  | 1.5                          | Zero                    |

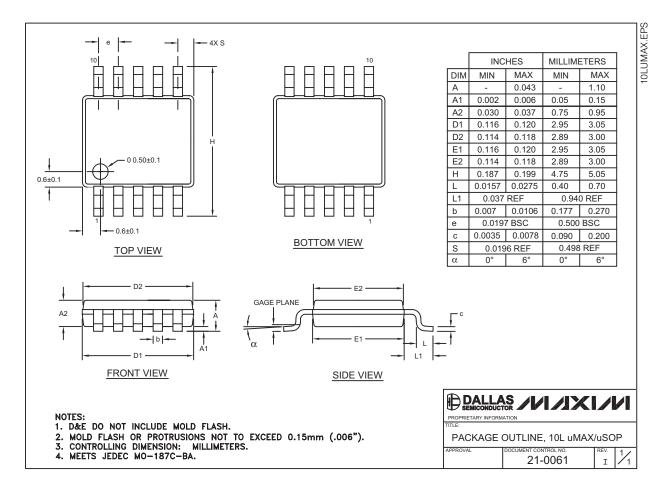

## Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

#### Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_

© 2004 Maxim Integrated Products

Printed USA

is a registered trademark of Maxim Integrated Products.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# Maxim Integrated:

| MAX5200ACUB+ | MAX5200ACUB+1 | MAX5200AEUB+ | MAX5200AEUB+T | MAX5200BEUB+ | MAX5200BEUB+T |

|--------------|---------------|--------------|---------------|--------------|---------------|

| MAX5201ACUB+ | MAX5201ACUB+T | MAX5201AEUB+ | MAX5201AEUB+T | MAX5201BEUB+ | MAX5201BEUB+T |

| MAX5202ACUB+ | MAX5202ACUB+T | MAX5202AEUB+ | MAX5202AEUB+T | MAX5202BEUB+ | MAX5202BEUB+T |

| MAX5203ACUB+ | MAX5203ACUB+T | MAX5203AEUB+ | MAX5203AEUB+T | MAX5203BEUB+ | MAX5203BEUB+T |